|

|

突破硅半导体极限,1纳米工艺的晶体管已经诞生是怎么回事,是真的吗?2016年11月01日是本文发布时间是这个时间。下面一起来看看到底怎么回事吧。

突破硅半导体极限,1纳米工艺的晶体管已经诞生

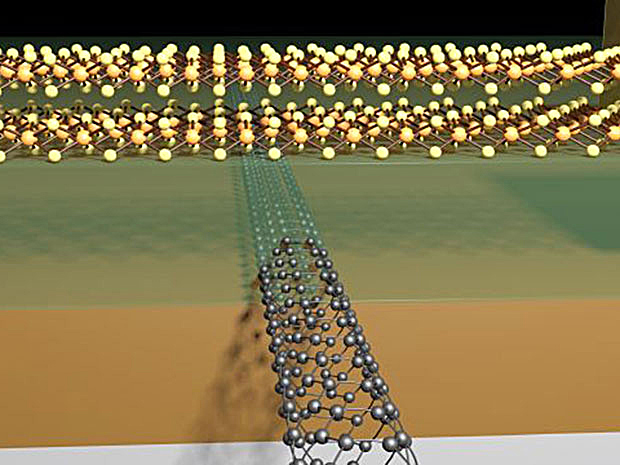

科学家利用二硫化钼和碳纳米管,制成了栅极线宽仅有1纳米的晶体管

关于“史上最小尺寸晶体管”称号的归属问题一直存在着争议,不过,如今一个由美国科学家主导的科研团队可以非常自豪而肯定地宣称,他们在这份追求技术极限的榜单上占据了领先位置。更重要的是,他们实现的这一项技术,有可能转化为实际产品,而不仅仅是一个只能存在于实验室中的发明创造。

这个小组的研究人员利用二硫化钼(molybdenum disulfide)和碳纳米管(carbon nanotube),成功地研制出栅极线宽仅为1纳米的晶体管,这不仅仅大幅度超越了目前最为先进的商用芯片中晶体管20纳米的栅极线宽,更是突破了硅基晶体管5纳米栅极线宽的理论物理极限。根据之前的预测,由于受制于到硅基晶体管尺寸的物理极限,预言晶体管尺寸不断缩小的摩尔定律可能会在2021年终结。而这项新研究也许预示着,在纳米材料的助力下,晶体管的微缩之路还可以继续走下去。

这项成果发表在《科学》(Science)杂志上,研究人员主要来自于美国能源部劳伦斯伯克利国家实验室、斯坦福大学和得克萨斯州立大学达拉斯分校,他们使用二硫化钼材料作为晶体管的沟道,而晶体管的栅极则由单壁碳纳米管(single-walled carbon nanotube)构成。

多种纳米材料的结合使得晶体管栅极线宽可以进一步减小。这里我们简要介绍一下晶体管的工作原理,晶体管主要由三部分组成——源极(source)、漏极(drain)、栅极(gate),源、漏两极位于导电沟道两端,电荷经由沟道在源、漏之间运动从而形成电流,栅极则一般位于沟道上方,用于控制沟道的开关,源、漏之间电流的有和无就表示着计算机中所用的二进制信号的1和0。

通常来说,硅是比二硫化钼更合适的沟道材料,这是因为电子在硅沟道中运动所受到的散射更少,即硅的电阻率较低,而在二硫化钼材料中,电子的输运相对困难。但是,当栅极线宽缩小到5纳米以下时,这些原本有利的物理特性开始阻碍硅基器件的进一步微缩。在低于5纳米的尺度下,材料的量子隧穿特性开始显现,这使得电子无论沟道开或关都可以轻易地在源极和漏极之间运动。这样的结果是,我们无法再通过栅极电压的变化来控制器件的开关,也就无法实现电路的逻辑功能了。

而电子在二硫化钼材料中的迁移速度更低,这对于5纳米以上宽度的二硫化钼材料来说是一种劣势,而在栅极线宽进一步缩短时就成为了它的优势,这使得栅极可以更有效地控制沟道中电子的流动。

解决了沟道材料的选择问题,研究人员要面临的下一个难题是使用什么样的材料来制作那么短的栅极,传统的光刻(lithography)工艺无法满足要求,而通过使用碳纳米管材料,我们可以直接跳过光刻的问题来实现这一目标。

“要制造1纳米长的金属栅极是相当困难的,尤其是在用于学术研究的实验室里。”来自伯克利实验室材料科学分部(Berkeley Lab’s Materials Science Division)的电子材料项目的首席研究员Ali Javey在一次电子邮件采访中解释道,“而利用碳纳米管的固有特性,比如说良好的导电性能,以及圆滑无棱角,没有边缘粗糙度(edge roughness),利用碳纳米管,我们可以很方便制造出1纳米的栅极。”

这样的科研成果,往往会引起人们超出实际的期望,而Javey也对这样的情况有所准备,他在新闻稿中提到,“这只是一次概念验证,目前为止,我们还没有将这些新型器件集成到一个实际芯片中去,还没有进行成千上万次的重复性试验,另外,我们也还没有开发出相应的自对准工艺来降低器件的寄生电阻(parasitic resistance)。”

尽管如此,看到5纳米的栅极线宽极限可能被突破依然是令人感到兴奋的,这项研究至少可以说明半导体之路并未到达尽头。

撰文:Dexter Johnson

翻译:刘卓

审校:王舟

原文链接:http://spectrum.ieee.org/nanoclast/semiconductors/devices/onenanometer-gate-dimensions-for-transistors-have-been-achieved |

|